PathFinder-SC (Semiconductor) |

The All-Encompassing ESD Solution for Analysis, Debug and Performance Optimization of IC layout and Circuits

In addition to verification and sign-off IP and full-chip SoC designs for integrity and performance, the software also identifies design issues that can cause chip or IP failure from charged-device model (CDM), human body model (HBM) or other related ESD events.

PathFinder is signoff certified by all major foundries, ensuring that interconnect parasitics, HBM/CDM ESD automation and current-density checks are silicon accurate. It’s layout-based GUI facilitates rapid root cause detection and intuitive debugging interfaces.

PathFinder | Core Technologies

Debugging Capabilities for Hundreds of Power Modes, Simultaneously.

Pathfinder Core Features Include:

- HBM/CDM ESD Events

- Silicon-Correlated Accuracy

- Root Cause Detection

- Single Pass Simulation

- Capacity and Performance

- Library to SoC-Level

- Cloud-Native Elastic Compute

Semiconductor Solutions | A Smarter Approach to SoC Testing

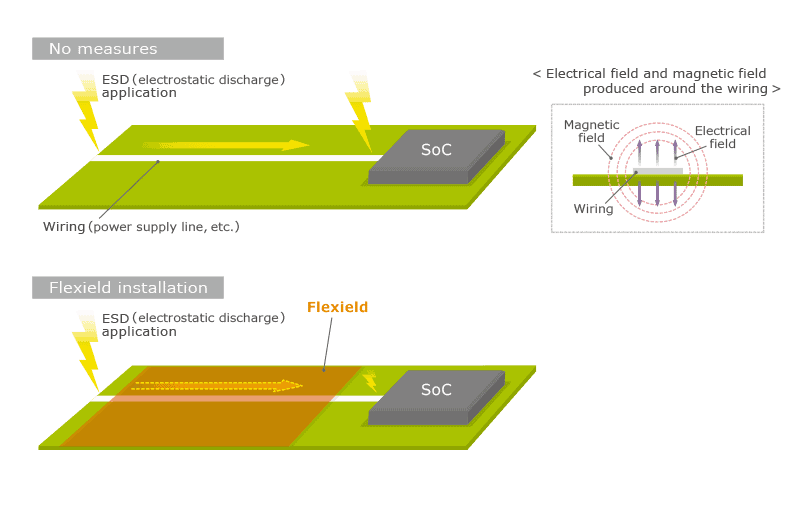

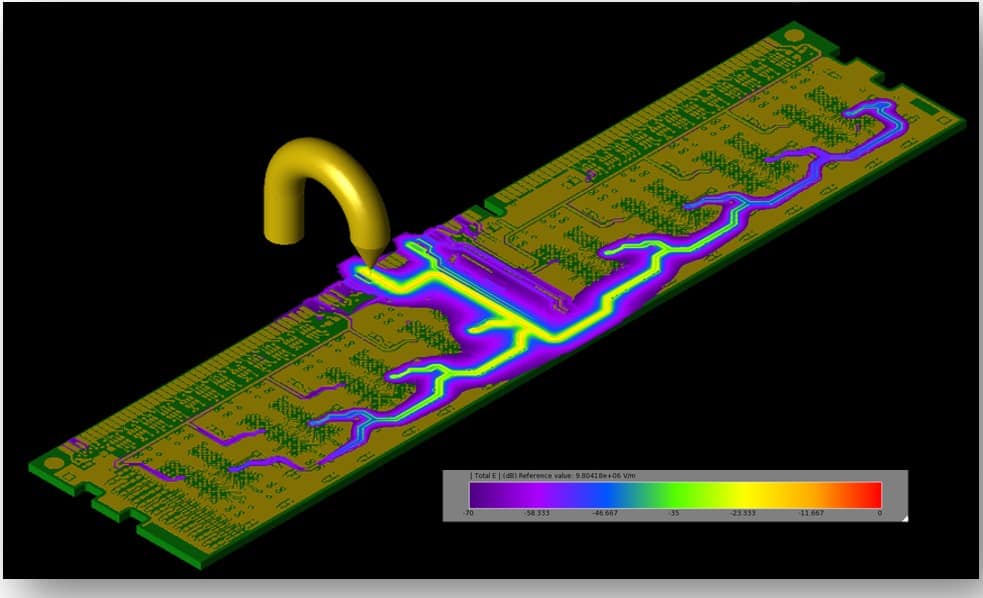

PathFinder-SC imitates human body model (HBM) and charged-device model (CDM) ESD events by propagating the zap current through power/ground networks to isolate layout bottlenecks. The software models the injection of current into any pad and interconnect pathway to identify pin-clamp-pin paths that can’t handle or regulate high ESD currents.

- PathFinder-SC readily identifies layout issues and connectivity imbalances that may lead to ESD failure.

- Examples include bumps not connected to ESD clamps, or clamps not hooked up to power/ground.

- By traversing each conduction pathway between any two relevant points on the chip, PathFinder-SC verifies connectivity robustness and checks electrical characteristics against foundry- or user-specified limits.

- In addition, pass-fail reports can be cross-probed to the layout.

- PathFinder-SC’s dynamic simulations using SPICE models and TLP curves at picosecond resolution offer engineers and designers silicon-correlated accuracy, which serves to minimize design risk.

- Clamps with snap-back regularly have convergence issues in SPICE; however, PathFinder-SC’s simulation engine is customized to regulate snap-back and accurately model ESD device triggering.

- In terms of veritableness and industry credibility, PathFinder’s results have been correlated with silicon by multiple foundries and customers across all of North America.

- PathFinder-SC’s integrated data modeling, extraction and simulation engine offers a streamlined, single-pass ESD use model.

- This includes setting up ESD cadence, performing extraction and ESD simulations, analyzing root causes, and providing fix and optimization feedback — all within a single-tool environment.

- The software uses industry-standard data formats (GDS, DEF) and offers considerable flexibility in specifying rules and parameters to be checked.

- PathFinder-SC checks ESD integrity on IP and large SOCs with more than 100 million instances.

- The software handles hundreds of power/ground/signal nets and performs resistance and current density checks in a single simulation.

- Full-chip ESD simulations can be completed in a few hours to a single day, depending on size.

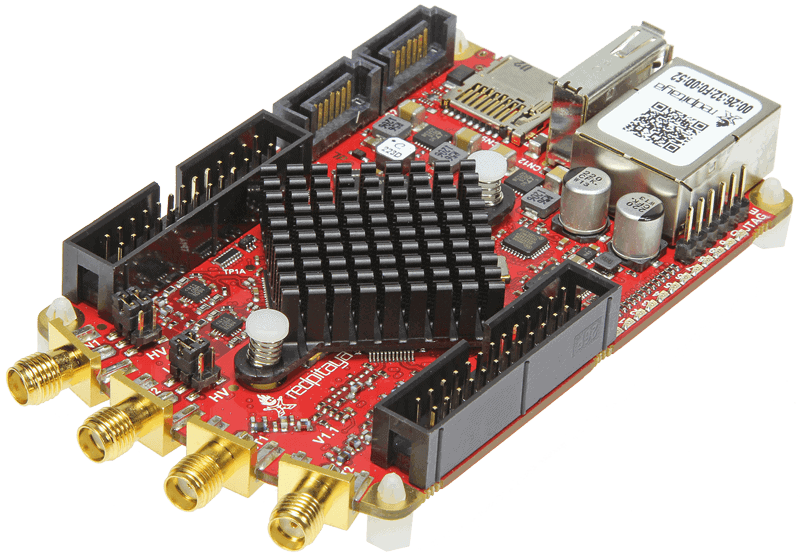

- In addition, PathFinder-SC is built on an elastic compute, cloud-native infrastructure to handle ultra-large designs.

- PathFinder-SC is built on the SeaScape big data analytics platform that is designed for cloud execution on 1,000s of CPU cores with near linear scalability and extremely high capacity, with low memory per core.

- This enables engineers to isolate high current hotspots at the standard cell level, IP level and full-chip level to avoid reliability issues.

- PathFinder-SC’s built-in modeling capability is based on the chip ESD compact model (CECM), which allows for detailed ESD analysis at any level, from standard cell to full-chip.

- CECM includes a PG model, clamp devices and an optional current signature. This precision-based modeling meets the highest reliability needs for any design.