Channel Modeling

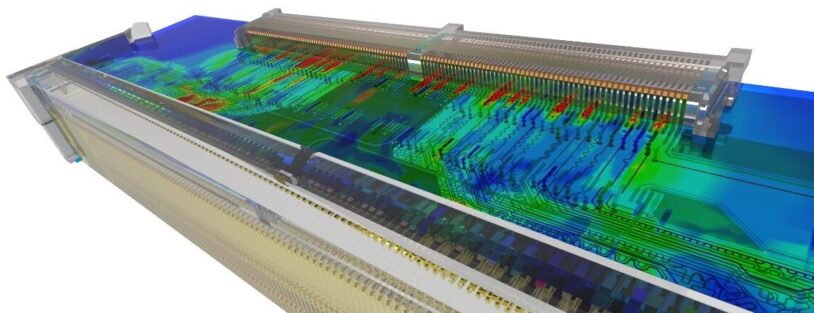

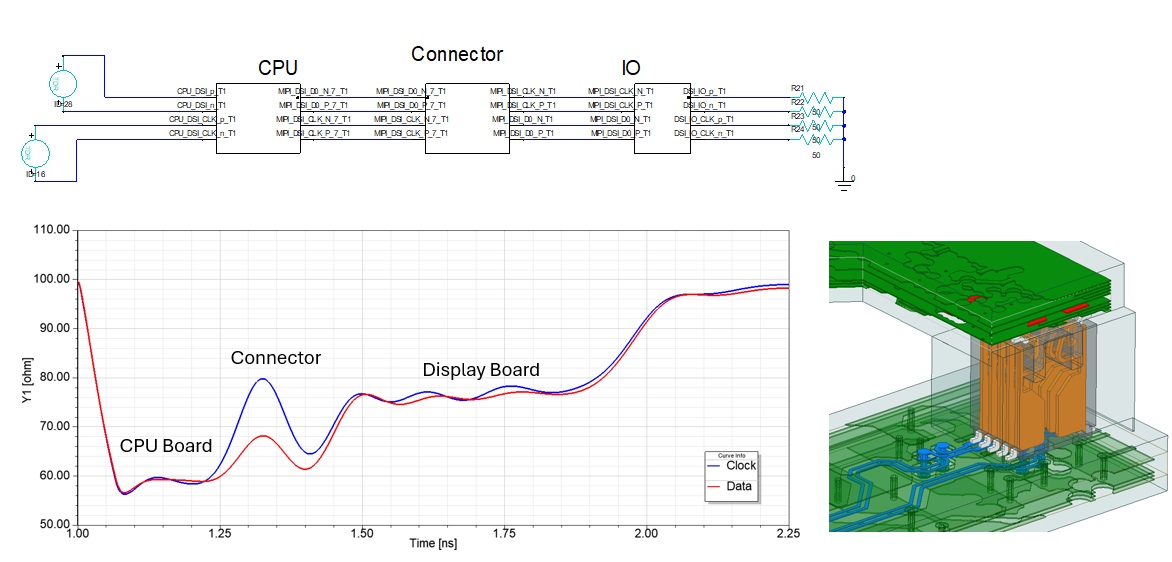

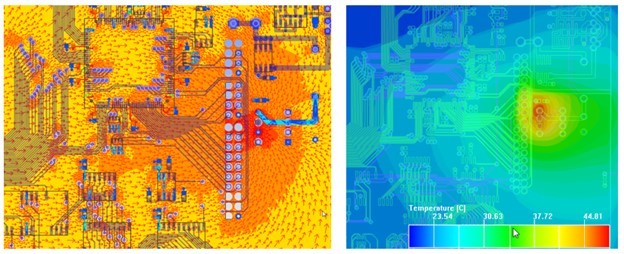

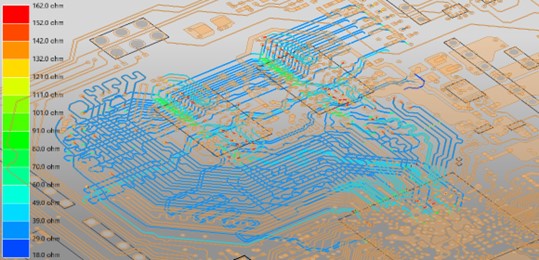

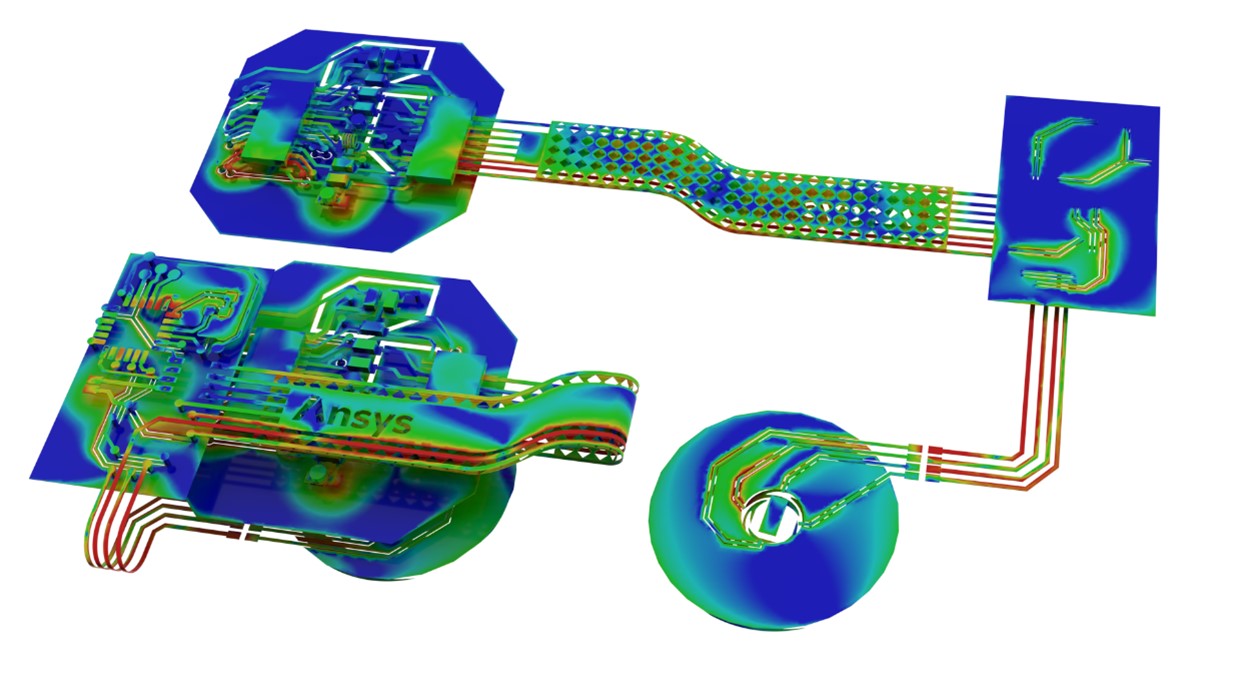

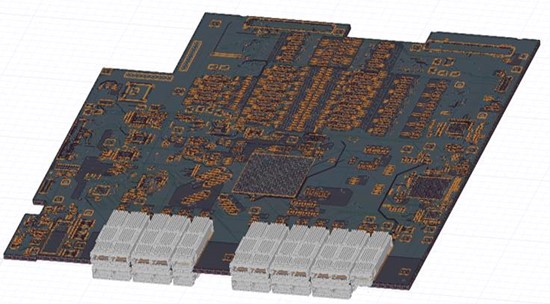

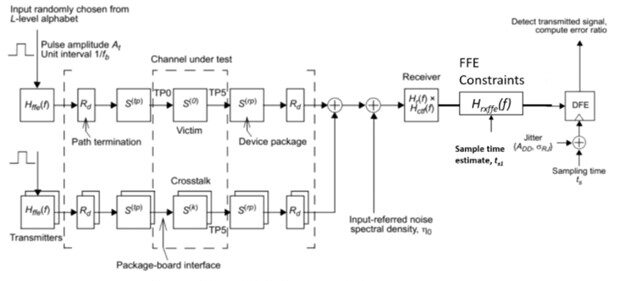

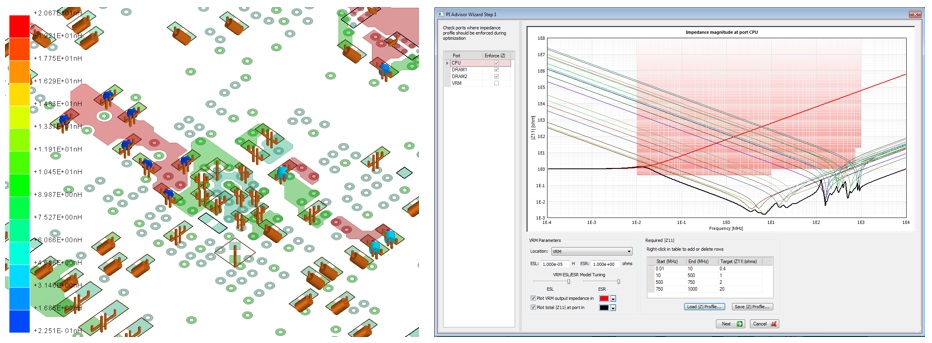

While PCB layouts are common targets for modeling and loss analysis, a full channel model is often desired to capture all interface effects seen by a signal, such as connector, IC, and cable interfaces on board. When these components have model data, either as CAD files or encrypted HFSS components, SimuTech Group will explicitly analyze the full effects of these interfaces.

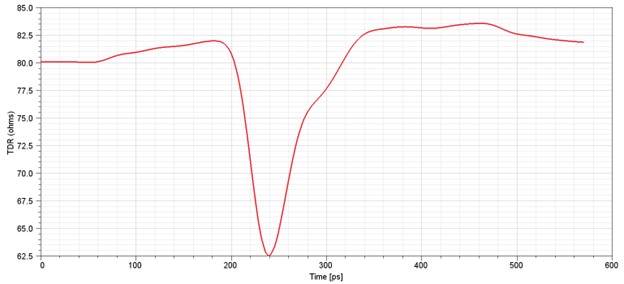

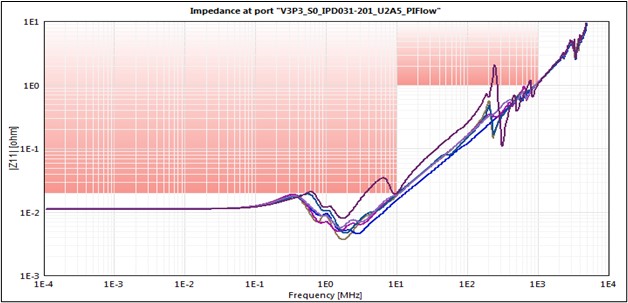

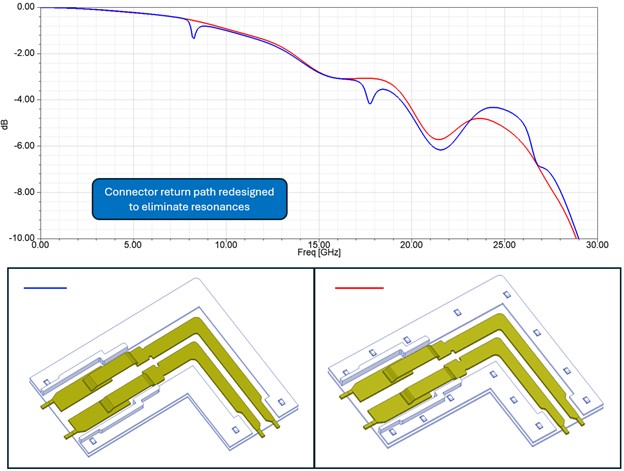

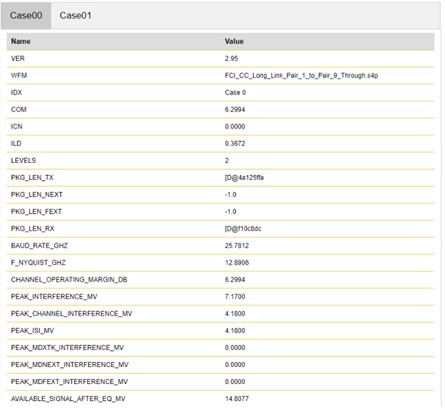

It is fairly common for vendors to only provide touchstone or SPICE models of their components. In this case, a channel model is built from various full-wave extractions of the transmission line and these component models cascaded in a single analysis, such as the mezzanine connector interface below demonstrating each element’s contribution to the TDR impedance profile.

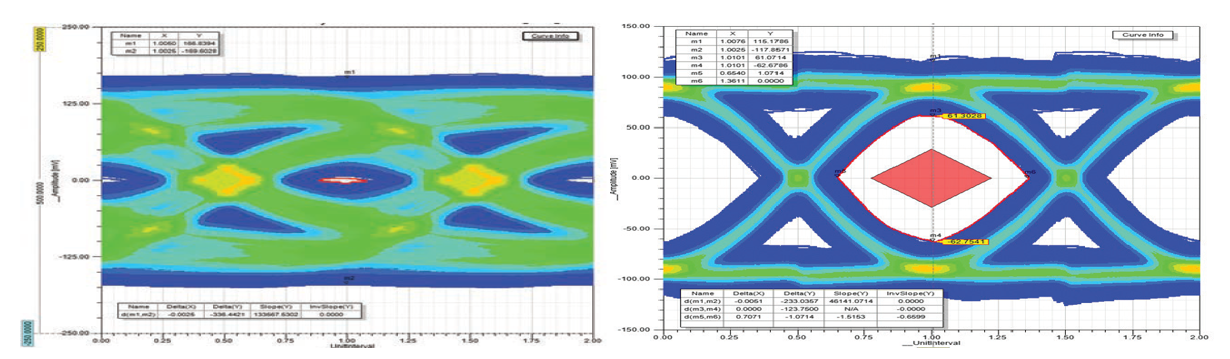

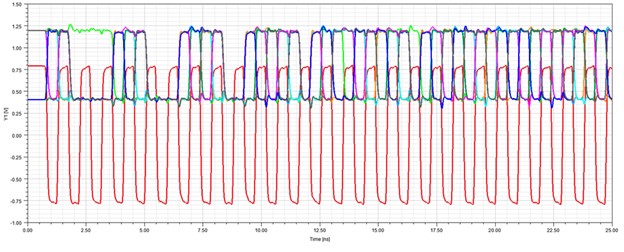

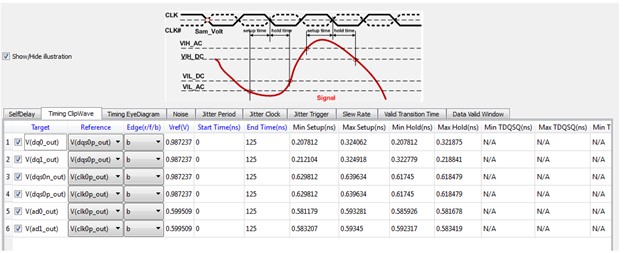

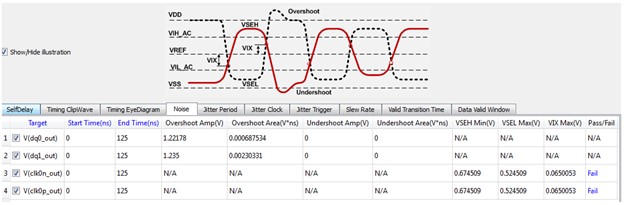

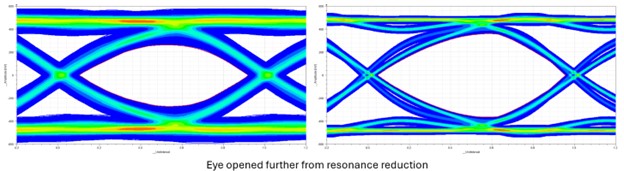

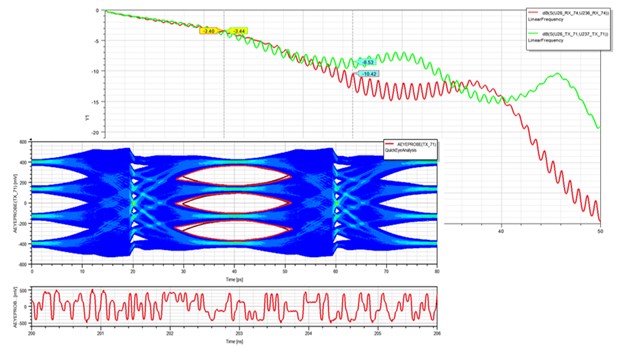

Once a channel model is assembled, driver and receiver models can be applied to produce projected time-domain output waveforms (at package pins or on-die) and directly relate the s-parameters and TDR results to an eye diagram. Using IBIS-AMI models and solutions, SimuTech Group engineers can predict bit error rate (BER), eye opening with and without equalization, temperature and voltage-dependent corner cases, power supply deviation, clock jitter, and more.