Introduction

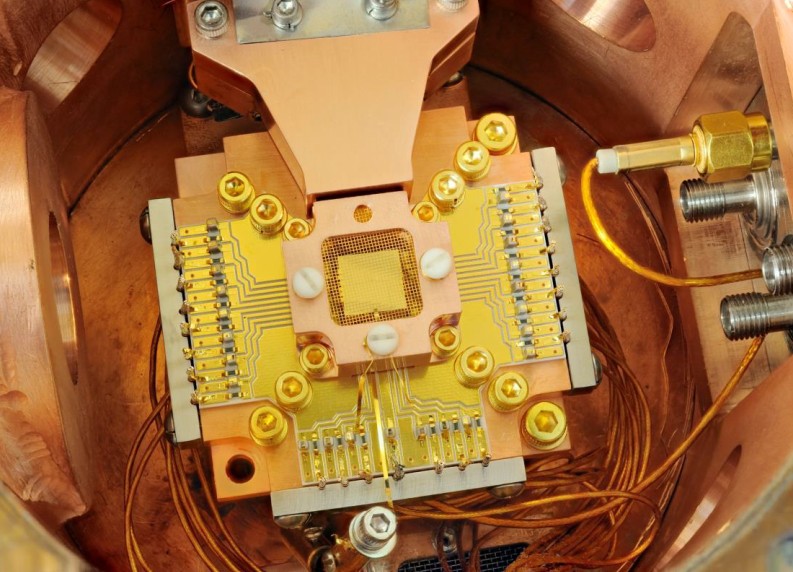

Quantum computing promises breakthroughs in fields like quantum chemistry, cryptography, and optimization. Among the various architectures, ion trap quantum computers (or “trapped ion” quantum computers) stand out for their long coherence times, high gate fidelity, and modular design. However, scaling these systems from laboratory prototypes to large-scale quantum processors introduces significant engineering challenges. The good news is that many of these challenges can be addressed using advanced multiphysics simulation tools.

Why Ion Trap Quantum Computers?

Trapped-ion qubits offer several advantages:

- Long coherence times (seconds to minutes), enabling complex algorithm execution.

- Identical qubits, since each ion is an atom, eliminating fabrication variability.

- High gate fidelity, with single-qubit operations exceeding 99.9% accuracy.

- Operation in low-noise environments under ultra-high vacuum and strong electromagnetic confinement.

Despite these benefits, scaling introduces hurdles in electromagnetic design, thermal management, and photonic integration.

Like what you’re reading? Watch the on-demand webinar.

Go deeper with our “Addressing Scaling Challenges of Ion Trap Quantum Computers with Ansys Multiphysics Software” webinar. See how Ansys Maxwell, HFSS, SIwave, Icepak, and Lumerical are used to model trapping potentials, manage electric field noise and heating, and optimize optical delivery and photonic interconnects for scalable ion trap architectures.

Key Engineering Challenges and Simulation Strategies for Ion Trap Quantum Computers

- Electromagnetic Design for Ion Traps

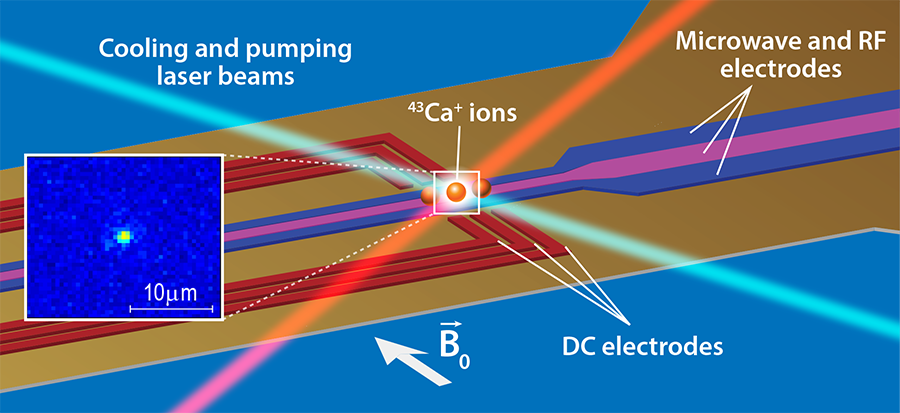

Ion confinement relies on precise electric and magnetic fields generated by DC and RF electrodes. As systems grow, engineers must:

- Optimize electrode geometry for stable trapping potentials.

- Minimize RF power dissipation and EMI.

- Model parasitic capacitances and signal integrity across complex boards.

Ansys Maxwell and HFSS provide complementary solvers:

- Maxwell handles electrostatic and magnetostatic problems for DC and quasi-static RF fields.

- HFSS solves full-wave, high-frequency interactions, critical for RF traces and integrated circuits.

Adaptive meshing ensures accuracy across scales, while Mesh Fusion enables efficient simulation of nanometer-scale chip features alongside millimeter-scale trap structures.

- Thermal and Reliability Analysis

Scaling introduces significant heat loads from RF currents and control electronics. Thermal cycling between vacuum and ambient conditions can degrade reliability.

Simulation workflow:

- Q3D Extractor for current distribution and parasitic analysis.

- Icepak for airflow and convective cooling strategies.

- Ansys Mechanical and Sherlock for fatigue and reliability predictions under thermal cycling.

Example: Bond wire analysis under 1 A load showed localized heating to 30°C, mitigated by airflow cooling and optimized wire count.

- Photonic Integration

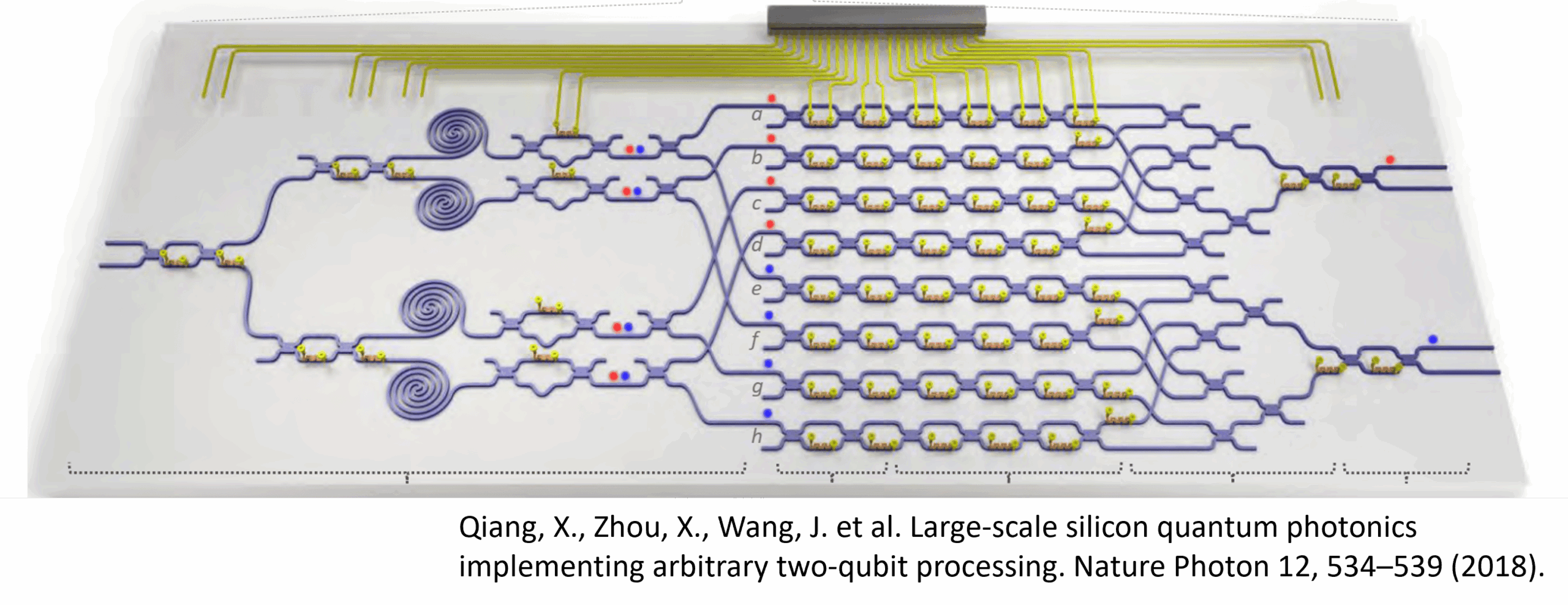

Reducing system footprint requires moving bulky optical setups on-chip:

- Integrated waveguides for laser delivery and Doppler cooling.

- On-chip detectors like single-photon avalanche diodes for state readout.

- Fiber-to-chip couplers and micro-ring resonators for quantum networking.

Ansys Lumerical enables design of photonic components, modeling absorption rates, dark currents, and coupling efficiency.

System-Level Considerations

Large-scale integration demands co-simulation across domains:

- SIwave for signal integrity on complex boards.

- PyAnsys for Python-based automation and data exchange with quantum circuit optimization workflows.

Conclusion

Scaling ion trap quantum computers is as much an engineering challenge as a physics problem. By leveraging multiphysics simulation—electromagnetic, thermal, mechanical, and photonic—engineers can design robust, scalable architectures that accelerate quantum technology adoption.